# EC325 Microprocessors IA32,IA32e Environment

Yasser F. O. Mohammad

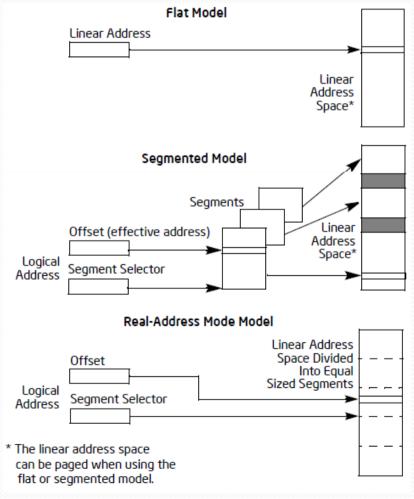

#### **REMINDER 1:IA32 Memory Models**

#### Operating and Memory Mode

- Protected

- All available (32 bits)

- Real-Address Mode

- Only Flat with 16 Bit Registers

- SMM

- Separate Read Address Space

- Compatibility Mode

- All available (32 bits)

- 64-bit

- Segmentation is usually Disabled

#### IP in different modes

|                            | Bits 63:32     | Bits 31:16 | Bits 15:0 |

|----------------------------|----------------|------------|-----------|

| 16-bit instruction pointer | Not Modified   |            | IP        |

| 32-bit instruction pointer | Zero Extension | EIP        |           |

| 64-bit instruction pointer | RIP            |            |           |

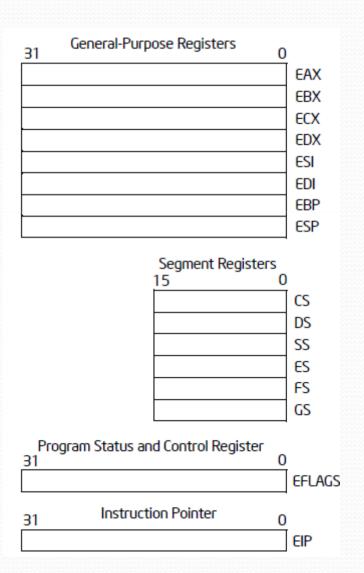

#### GPRs (32 bits)

| 31 | 16 | 15 | 8  | 7  | 0 | 16-bit | 32-bit |

|----|----|----|----|----|---|--------|--------|

|    |    | AH |    | AL |   | AX     | EAX    |

|    |    | BH |    | BL |   | BX     | EBX    |

|    |    | CH |    | CL |   | CX     | ECX    |

|    |    | DH |    | DL |   | DX     | EDX    |

|    |    |    | В  | P  |   |        | EBP    |

|    |    |    | S  | l  |   |        | ESI    |

|    |    |    | D  | I  |   |        | EDI    |

|    |    |    | SI | Р  |   |        | ESP    |

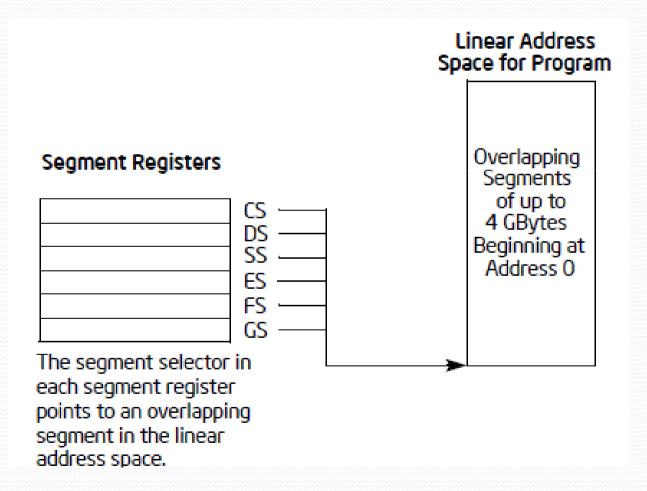

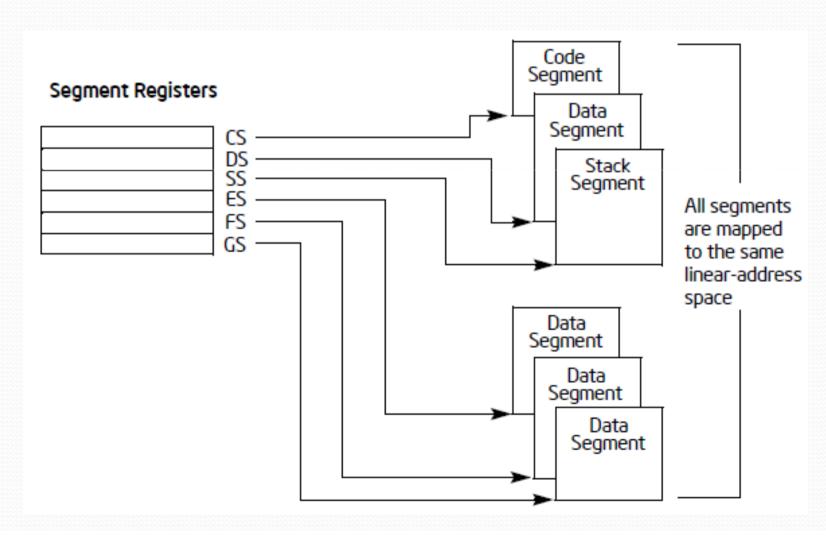

## Use of Segment Registers Flat Memory

## Use of Segment Registers Segmented Mode

#### Use of GPRs

- EAX Accumulator for operands and results data

- **EBX** Pointer to data in the DS segment

- ECX Counter for string and loop operations

- **EDX** I/O pointer

- **ESI** Pointer to data in the segment pointed to by the DS register; source pointer for string operations

- **EDI** Pointer to data (or destination) in the segment pointed to by the ES register; destination pointer for string operations

- ESP Stack pointer (in the SS segment)

#### **GRP** names

|    | General-Purpo | se Regist | ers |   |        |        |

|----|---------------|-----------|-----|---|--------|--------|

| 31 | 16            | 15 8      | 3 7 | 0 | 16-bit | 32-bit |

|    |               | АН        | AL  |   | AX     | EAX    |

|    |               | BH        | BL  |   | BX     | EBX    |

|    |               | CH        | CL  |   | CX     | ECX    |

|    |               | DH        | DL  |   | DX     | EDX    |

|    |               | E         | 3P  |   |        | EBP    |

|    |               | •         | SI  |   |        | ESI    |

|    |               | I         | DI  |   |        | EDI    |

|    |               | 9         | SP  |   |        | ESP    |

#### 64-bit registers

| Register Type        | Without REX                            | With REX                                              |

|----------------------|----------------------------------------|-------------------------------------------------------|

| Byte Registers       | AL, BL, CL, DL, AH, BH, CH, DH         | AL, BL, CL, DL, DIL, SIL, BPL, SPL,<br>R8L - R15L     |

| Word Registers       | AX, BX, CX, DX, DI, SI, BP, SP         | AX, BX, CX, DX, DI, SI, BP, SP, R8W -<br>R15W         |

| Doubleword Registers | EAX, EBX, ECX, EDX, EDI, ESI, EBP, ESP | EAX, EBX, ECX, EDX, EDI, ESI, EBP,<br>ESP, R8D - R15D |

| Quadword Registers   | N.A.                                   | RAX, RBX, RCX, RDX, RDI, RSI,<br>RBP, RSP, R8 - R15   |

- Same instruction cannot access a legacy high byte and a new byte register

- Operations in parts of registers keep the rest of them untouched

#### **EFLAGS**

|                                                                                                                                                                                                                                         | 31 30                                                                                                                   | 29                                                               | 28 27                                                                           | 26 2             | 5 24 | 23 2 | 2 2    | 1 20   | 19     | 18 | 17 | 16 | 15 | 14     | 13 12       | 11     | 10     | 9      | 8 | 7 | 6 | 5 | 4 | 3 | 2      | 1 | 0      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------|------|------|--------|--------|--------|----|----|----|----|--------|-------------|--------|--------|--------|---|---|---|---|---|---|--------|---|--------|

|                                                                                                                                                                                                                                         | 0 0                                                                                                                     | 0                                                                | 0 0                                                                             | 0 0              | 0    | 0    | ם<br>נ | V<br>P | V<br>F | A  | V  | R  | 0  | N<br>T | 0<br>P<br>L | O<br>F | D<br>F | I<br>F | T | S | Z | 0 | A | 0 | P<br>F | 1 | C<br>F |

| X ID Flag (ID X Virtual Inter X Virtual Inter X Alignment ON X Virtual-808 X Resume Food X I/O Privileg S Overflow Food C Direction Food X Interrupt End X Trap Flag (S Sign Flag (S Auxiliary Communication S Parity Flag S Carry Flag | errupt<br>rrupt  <br>Checl<br>6 Moo<br>lag (F<br>sk (N<br>e Lev<br>Flag (I<br>nable<br>TF) –<br>SF) –<br>arry F<br>(PF) | : Pe<br>Flag<br>k (A<br>tde (A<br>T)—<br>rel (DF)<br>DF)<br>Flag | endiii<br>g (V<br>AC) -<br>(VM<br>(IOP<br>)———————————————————————————————————— | ng (\vert   F) — | 'IP) |      |        |        |        |    |    |    |    |        |             |        |        |        |   |   |   |   |   |   |        |   |        |

| S Indicates a<br>C Indicates a<br>X Indicates a                                                                                                                                                                                         | Cont                                                                                                                    | rol                                                              | Flag                                                                            |                  |      |      |        |        |        |    |    |    |    |        |             |        |        |        |   |   |   |   |   |   |        |   |        |

#### Flag Meaning

- CF: Set if there is a carry

- PF: Set if least significant byte of result has even ones

- AF: Set if an arithmetic operation generates carry/borrow in bit 3 (BCD)

- ZF: Set if zero

- SF: Set if MSB is 1

- OF: Set on overflow (2's)

- DF: Direction in string operations

- TF: Single step during debugging

- IF: Interrupt enable

- IOPL: privilege level

- NT: Nested task

- RF: Used by debugger

- VM: Virtual 8o86 mode

- AC: Alignment Checks

- ID: can I ask your name??

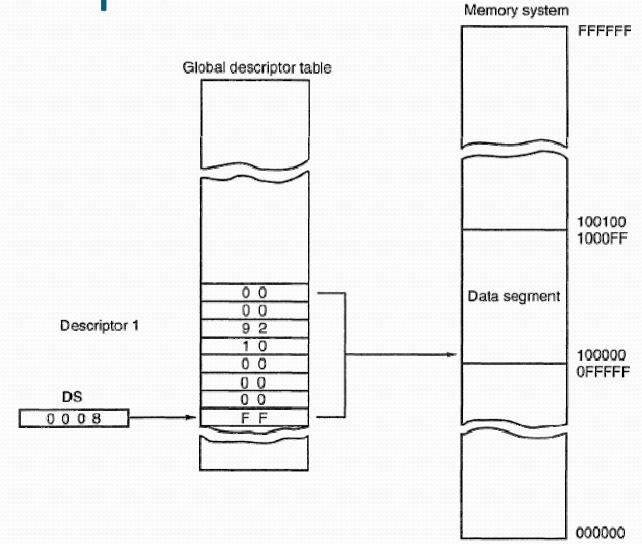

#### Protected Mode Addressing

- Segment registers store selectors rather than base address (bases are not really bases!!!!)

- 8K global descriptors

- 8K local descriptors

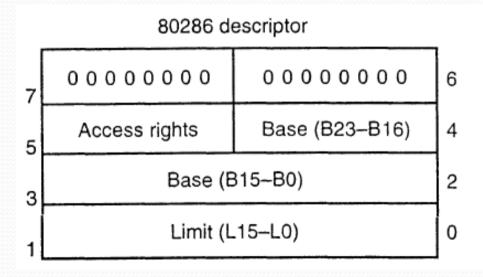

- Descriptor = 8 bytes

#### **Descriptor Format**

80386/80486/Pentium/Pentium Pro descriptor

| 7 | Base (B31-B24) | G             | D | 0 | A<br>V | Limit<br>(L19–L16) | 6 |  |  |  |  |

|---|----------------|---------------|---|---|--------|--------------------|---|--|--|--|--|

| 5 | Access rights  | Base (B23B16) |   |   |        |                    |   |  |  |  |  |

| 3 | Base (B15-B0)  |               |   |   |        |                    |   |  |  |  |  |

| 1 | Limit (L15-L0) |               |   |   |        |                    |   |  |  |  |  |

### Example

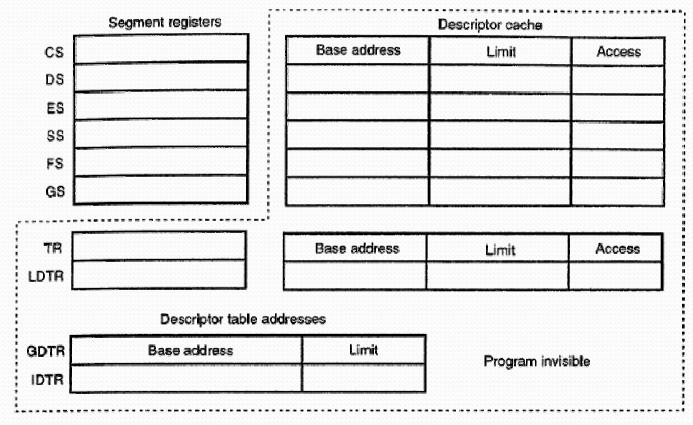

#### Program Invisible Registers

#### Notes:

- 1. The 80286 does not contain FS and GS nor the program-invisible portions of these registers.

- 2. The 80286 contains a base address that is 24-bits and a limit that is 16-bits.

- 3. The 80386/80486/Pentium/Pentium Pro contain a base address that is 32-bits and a limit that is 20-bits.

- 4. The access rights are 8-bits in the 80286 and 12-bits in the 80386/80486/Pentium.

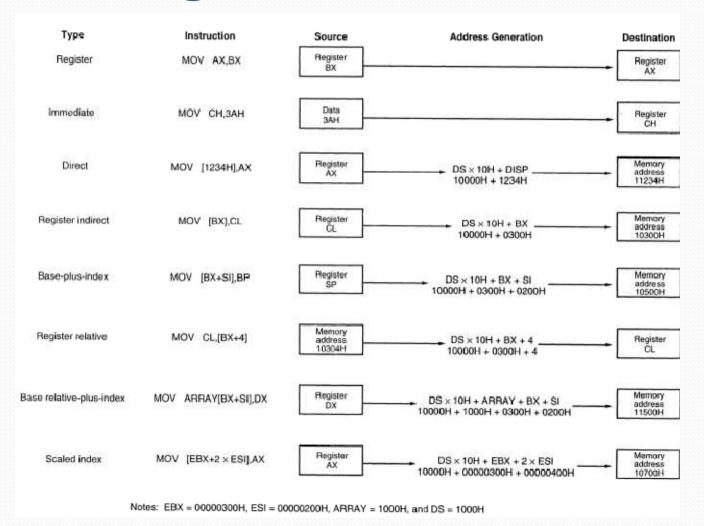

#### **Addressing Modes**